The CHASSIS SCC-501C-A (XE3) is developed on a 3 Parts /Panels.

- Monocarrier on bottom centre: All receiver functions + deflections

- Power supply (line synchronized) on the left side. with NEC uPC1394

- Control unit: M Unit on bottom left side.

SONY CX522

SONY TRINITRON KV-1882ME3 CHASSIS SCC-501C-A (XE3) Synchronized switch-mode power supply:

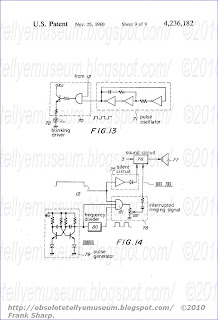

In a switch mode power supply, a first switching transistor is coupled to a primary winding of an isolation transformer. A second switching transistor periodically applies a low impedance across a second winding of the transformer that is coupled to an oscillator for synchronizing the oscillator to the horizontal frequency. A third winding of the transformer is coupled via a switching diode to a capacitor of a control circuit for developing a DC control voltage in the capacitor that varies in accordance with a supply voltage B+. The control voltage is applied via the transformer to a pulse width modulator that is responsive to the oscillator output signal for producing a pulse-width modulated control signal. The control signal is applied to a mains coupled chopper transistor for generating and regulating the supply voltage B+ in accordance with the pulse width modulation of the control signal.

The invention relates to switch-mode power supplies.

Some television receivers have signal terminals for receiving, for example, external video input signals such as R, G and B input signals, that are to be developed relative to the common conductor of the receiver. Such signal terminals and the receiver common conductor may be coupled to corresponding signal terminals and common conductors of external devices, such as, for example, a VCR or a teletext decoder.

To simplify the coupling of signals between the external devices and the television receiver, the common conductors of the receiver and of the external devices are connected together so that all are at the same potential. The signal lines of each external device are coupled to the corresponding signal terminals of the receiver. In such an arrangement, the common conductor of each device, such as of the television receiver, may be held "floating", or conductively isolated, relative to the corresponding AC mains supply source that energizes the device. When the common conductor is held floating, a user touching a terminal that is at the potential of the common conductor will not suffer an electrical shock.

Therefore, it may be desirable to isolate the common conductor, or ground, of, for example, the television receiver from the potentials of the terminals of the AC mains supply source that provide power to the television receiver. Such isolation is typically achieved by a transformer. The isolated common conductor is sometimes referred to as a "cold" ground conductor.

In a typical switch mode power supply (SMPS) of a television receiver the AC mains supply voltage is coupled, for example, directly, and without using transformer coupling, to a bridge rectifier. An unregulated direct current (DC) input supply voltage is produced that is, for example, referenced to a common conductor, referred to as "hot" ground, and that is conductively isolated from the cold ground conductor. A pulse width modulator controls the duty cycle of a chopper transistor switch that applies the unregulated supply voltage across a primary winding of an isolat ing flyback transformer. A flyback voltage at a frequency that is determined by the modulator is developed at a secondary winding of the transformer and is rectified to produce a DC output supply voltage such as a voltage B+ that energizes a horizontal deflection circuit of the television receiver. The primary winding of the flyback transformer is, for example, conductively coupled to the hot ground conductor. The secondary winding of the flyback transformer and voltage B+ may be conductively isolated from the hot ground conductor by the hot-cold barrier formed by the transformer.

ing flyback transformer. A flyback voltage at a frequency that is determined by the modulator is developed at a secondary winding of the transformer and is rectified to produce a DC output supply voltage such as a voltage B+ that energizes a horizontal deflection circuit of the television receiver. The primary winding of the flyback transformer is, for example, conductively coupled to the hot ground conductor. The secondary winding of the flyback transformer and voltage B+ may be conductively isolated from the hot ground conductor by the hot-cold barrier formed by the transformer.

It may be desirable to synchronize the operation of the chopper transistor to horizontal scanning frequency for preventing the occurrence of an objectionable visual pattern in an image displayed in a display of the television receiver.

It may be further desirable to couple a horizontal synchronizing signal that is referenced to the cold ground to the pulse-width modulator that is referenced to the hot ground such that isolation is maintained.

A synchronized switch mode power supply, embodying an aspect of the invention, includes a transfromer having first and second windings. A first switching arrangement is coupled to the first winding for generating a first switching current in the first winding to periodically energize the second winding. A source of a synchronizing input signal at a frequency that is related to a deflection frequency is provided. A second switching arrangement responsive to the input signal and coupled to the second winding periodically applies a low impedance across the energized second winding that by transformer action produces a substantial increase in the first switching current. A periodic first control signal is generated. The increase in the first switching current is sensed to synchronize the first control signal to the input signal. An output supply voltage is generated from an input supply voltage in accordance with the first control signal.

winding for generating a first switching current in the first winding to periodically energize the second winding. A source of a synchronizing input signal at a frequency that is related to a deflection frequency is provided. A second switching arrangement responsive to the input signal and coupled to the second winding periodically applies a low impedance across the energized second winding that by transformer action produces a substantial increase in the first switching current. A periodic first control signal is generated. The increase in the first switching current is sensed to synchronize the first control signal to the input signal. An output supply voltage is generated from an input supply voltage in accordance with the first control signal.SONY TRINITRON KV-1882ME3 CHASSIS SCC-501C-A (XE3) SONY DST EHT FBT TRANSFORMER Bobbin structure for high voltage transformers EHT Output.

A coil bobbin for a fly-back transformer or the like having a bobbin proper. A plurality of partition members or flanges are formed on the bobbin proper with a slot between adjacent ones. At least first and second coil units are formed in the bobbin proper, each having several slots, formed between the flanges, and first and second high voltage coils are wound on the first and second coil units in opposite directions, respectively. A rectifying means is connected in series to the first and second coil units, and a cut-off portion or recess is provided on each of the partition members. In this case, a wire lead of the coil units passes from one slot to an adjacent slot through the cut-off portion which is formed as a delta groove, and one side of the delta groove is corresponded to the tangent direction to the winding direction.

1. A fly-back transformer comprising a coil bobbin comprising a plurality of parallel spaced discs with a first adjacent plurality of said disc formed with delta shaped slots having first edges which extend tangentially to a first winding direction and a first winding wound on said first adjacent plurality of said discs in said first winding direction, a second adjacent plurality of said discs formed with delta shaped slots having first edges which extend tangentially to a second winding direction opposite said first winding direction and a second winding wound on said second adjacent plurality of said discs in said second winding direction, a third adjacent plurality of said discs formed with delta shaped slots having first edges which extend tangentially to said first winding direction and a third winding wound on said third adjacent plurality of said discs in said first winding direction and said second plurality of adjacent discs mounted between said first and third plurality of adjacent discs. 2. A fly-back transformer according to claim 1 wherein adjacent ones of said first adjacent plurality of discs are mounted such that their delta shaped slots are orientated 180 degrees relative to each other. 3. A fly-back transformer according to claim 2 including a first winding turning partition mounted between said first and second adjacent plurality of discs and formed with grooves and notches for changing winding direction between said first and second windings and a second winding turning partition mounted between said second and third adjacent plurality of discs and formed with grooves and notches for changing the winding direction between said second and third windings. 4. A fly-back transformer according to claim 3 wherein said first and second winding turning partitions are formed with winding guiding slots for guiding the winding between the first, second and third adjacent plurality of discs. 5. A fly-back transformer according to claim 2 including a first rectifying means connected between one end of said first winding and one end of said second winding, and a second rectifying means connected between the second end of said second winding and one end of said third winding. 6. A fly-back transformer according to claim 5 wherein the second end of said first winding is grounded and a third rectifying means connected between the second end of said third winding and an output terminal.

BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates generally to a bobbin structure for high voltage transformers, and is directed more particularly to a bobbin structure for high voltage transformer suitable for automatically winding coils thereon.

2. Description of the Prior Art

In the art, when a wire lead is reversely wound on a bobbin se parately at every winding block, a boss is provided at every winding block and the wire lead is wound on one block, then one end of the wire lead is tied to the boss where it will be cut off. The end of the wire lead is tied to another boss, and then the wire lead is wound in the opposite direction. Therefore, the prior art winding method requires complicated procedures and the winding of the wire lead cannot be rapidly done and also the winding can not be performed automatically. Further, the goods made by the prior art method are rather unsatisfactory and have a low yield.

parately at every winding block, a boss is provided at every winding block and the wire lead is wound on one block, then one end of the wire lead is tied to the boss where it will be cut off. The end of the wire lead is tied to another boss, and then the wire lead is wound in the opposite direction. Therefore, the prior art winding method requires complicated procedures and the winding of the wire lead cannot be rapidly done and also the winding can not be performed automatically. Further, the goods made by the prior art method are rather unsatisfactory and have a low yield.

OBJECTS AND SUMMARY OF THE INVENTION

Accordingly an object of the invention is to provide a coil bobbin for a fly-back transformer or the like by which a wire lead can be automatically wound on winding blocks of the coil bobbin even though the winding direction is different among the different winding blocks.

Another object of the invention is to provide a coil bobbin for a fly-back transformer or the like in which a bridge member and an inverse engaging device for transferring a wire lead from one wiring block to an adjacent wiring block of the coil bobbin and wiring the wire lead in opposite wiring directions between adjacent wiring blocks, and a guide member for positively guiding the wire lead are provided.

According to an aspect of the present invention, a coil bobbin for a fly-back transformer or the like is provided which comprises a plurality of partition members forming a plurality of slots, a first coil unit having several slots on which a first high voltage coil is wound in one winding direction, a second coil unit having several slots on which a second high voltage coil is wound in the other direction, a rectifying means connected in series to the first and second coil units, and a cut-off portion provided on each of the partition members, a wire lead passing from one slot to an adjacent slot through the cut-off portions, each of the cut-off portions being formed as a delta groove, and one side of the delta groove corresponding to a tangent to the winding direction.

The other objects, features and advantages of the present invention will become apparent from the following description taken in conjunction with the accompanying drawings through which the like reference numerals and letters designate the same elements and parts, respectively.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic diagram showing the construction of a fly-back transformer;

FIG. 2 is a connection diagram showing an example of the electrical connection of the fly-back transformer shown in FIG. 1;

FIG. 3 is a schematic diagram showing an example of a device for automatically winding a wire lead of the fly-back transformer on its bobbin;

FIG. 4 is a perspective view showing an example of the coil bobbin according to the present invention;

FIG. 5 is a plan view of FIG. 4;

FIGS. 6 and 7 are views used for explaining recesses or cut-off portions shown in FIGS. 4 and 5; and FIGS. 8A and 8B cross-sectional views showing an example of the inverse engaging means according to the present invention.

DESCRIPTION OF THE PREFERRED EMBODIMENT

When the high voltage winding of a fly-back transformer used in a high voltage generating circuit of a television receiver is divided into plural ones and then wound on a bobbin, the divided windings (divided coils) are connected in serie s through a plurality of rectifying diodes.

s through a plurality of rectifying diodes.

When the winding is divided into, for example, three portions, such as divided coils La, Lb and Lc, they are wound on a bobbin proper 1 from, for example, left to right sequentially in this order as shown in FIG. 1. In this case, if the divided coils La and Lc are selected to have the same sense of turn and the middle coil Lb is selected to have the opposite sense of turn from the coils La and Lc, the distance between the terminal end of coil La and the start of coil Lb and the distance between the terminal end of coil Lb and the start of coil Lc can be got relatively long. Therefore, diodes Da and Db can be mounted by utilizing the space above the block on which the middle coil Lb is wound as shown in FIG. 1, so that it becomes useless to provide spaces for diodes between the divided coils La and Lb and between the divided coils Lb and Lc and hence the bobbin proper 1 can be made compact.

FIG. 2 is a connection diagram showing the connection of the above fly-back transformer. In FIG. 2, reference numeral 2 designates a primary winding (Primary coil) of the fly-back transformer, reference letter L designates its high voltage winding (secondary coil), including divided coils La, Lb and Lc, 3 an output terminal, and 4 a lead wire connected to the anode terminal of a cathode ray tube (not shown), respectively.

An example of the bobbin structure according to the invention, which is suitable to automatically wind coils, which are different in sense of turn in each winding block as shown in FIG. 1, on the bobbin, will be hereinafter described with reference to the drawings.

FIG. 3 is a diagram showing an automatic winding apparatus of a wire lead on a coil bobbin. If it is assumed that the wire lead is wound in the order of w inding blocks A, B and C in FIG. 1 and the wire lead is wound on the block A with the bobbin proper 1 being rotated in the counter-clockwise direction as shown in FIG. 3, the relation between the bobbin proper 1 and the wire lead becomes as shown in FIG. 3. In this figure, reference numeral 6 designates a bobbin for feeding the wire lead.

inding blocks A, B and C in FIG. 1 and the wire lead is wound on the block A with the bobbin proper 1 being rotated in the counter-clockwise direction as shown in FIG. 3, the relation between the bobbin proper 1 and the wire lead becomes as shown in FIG. 3. In this figure, reference numeral 6 designates a bobbin for feeding the wire lead.

Turning to FIG. 4, an example 10 of the bobbin structure or coil bobbin according to the present invention will be described now. In this example, the winding blocks A, B and C for the divided coils La, Lb and Lc are respectively divided into plural slots or sections by plural partition members or flanges 11, and a cut-off portion or recess 12 is formed on each of the flanges 11 through which the wire lead in one section is transferred to the following winding section.

As shown in FIG. 6, each recess 12 is so formed that its one side extends in the direction substantially coincident with the tangent to the circle of the bobbin proper 1 and its direction is selected in response to the sense of turn of the winding or wire lead. In this case, the direction of recess 12 means the direction of the opening of recess 12, and the direction of recess 12 is selected opposite to the sense of turn of the wi nding in the present invention.

nding in the present invention.

Now, recesses 12A, which are formed in the winding block A, will be now described by way of example. The positions of recesses 12A formed on an even flange 11Ae and an odd flange 11A 0 are different, for example, about 180° as shown in FIGS. 6A and 6B. Since the bobbin proper 1 is rotated in the counter-clockwise direction in the winding block A and hence the sense of turn of the wire lead is in the clockwise direction, the recess 12A is formed on the even flange 11Ae at the position shown in FIG. 6A. That is, the direction of recess 12A is inclined with respect to the rotating direction of bobbin proper 1 as shown in FIG. 6A. In this case, one side 13a of recess 12A is coincident with the tangent to the circle of bobbin proper 1, while the other side 13b of recess 12A is selected to have an oblique angle with respect to the side 13a so that the recess 12A has a predetermined opening angle.

The opening angle of recess 12A is important but the angle between the side 13a of recess 12A and the tangent to the circle of bobbin proper 1 is also important in the invention. When the wire lead is bridged or transferred from one section to the following section through the recess 12A, the wire lead in one section advances to the following section in contact with the side 13a of recess 12A since the bobbin proper 1 is rotated. In the invention, if the side 13a of recess 12A is selected to be extended in the direction coincident with the tangent to the circle of bobbin proper 1, the wire lead can smoothly advance from one section to the next section without being bent.

In the invention, since the middle divided coil Lb is wound opposite to the divided coil La, a recess 12B provided on each of flanges 11B of the winding block B is formed to have an opening opposite to that of recess 12A formed in the winding block A as shown in FIGS. 6C and 6D.

As shown in FIG. 5, terminal  attaching recesses 14 are provided between the winding blocks A and B to which diodes are attached respectively. In the illustrated example of FIG. 5, a flange 15AB is formed between the flanges 11A 0 and 11B 0 of winding blocks A and B, and the recesses 14 are formed between the flanges 11A 0 and 15AB and between 15AB and 11B 0 at predetermined positions. Then, terminal plates 16, shown in FIG. 4, are inserted into the recesses 14 and then fixed there to, respectively. The terminal plates 16 are not shown in FIG. 5. Between the winding blocks B and C and between the blocks A and B, similar terminal attaching recesses 14 are formed, and terminal plates 16 are also inserted thereinto and then fixed thereto.

attaching recesses 14 are provided between the winding blocks A and B to which diodes are attached respectively. In the illustrated example of FIG. 5, a flange 15AB is formed between the flanges 11A 0 and 11B 0 of winding blocks A and B, and the recesses 14 are formed between the flanges 11A 0 and 15AB and between 15AB and 11B 0 at predetermined positions. Then, terminal plates 16, shown in FIG. 4, are inserted into the recesses 14 and then fixed there to, respectively. The terminal plates 16 are not shown in FIG. 5. Between the winding blocks B and C and between the blocks A and B, similar terminal attaching recesses 14 are formed, and terminal plates 16 are also inserted thereinto and then fixed thereto.

As described above, since the divided coil Lb is wound opposite to the divided coils La and Lc, it is necessary that the winding direction of the wire lead be changed when the wire lead goes from the block A to block B and also from the block B to block C, respectively.

Turning to FIG. 7, an example of the winding or wire lead guide means according to the present invention will be now described. In FIG. 7, there are mainly shown a bridge member for the wire lead and an inve rse member or means for the wire lead which are provided between the winding blocks A and B. At first, a bridge means 20 and its guide means 21, which form the bridge member, will be described. The bridge means 20 is provided by forming a cut-out portion or recess in the middle flange 15AB located between the winding blocks A and B. In close relation to the bridge means or recess 20, the guide means 21 is provided on a bridge section X A at the side of block A. This guide means 21 is formed as a guide piece which connects an edge portion 20a of recess 20 at the winding direction side to the flange 11A 0 of block A in the oblique direction along the winding direction through the section X A .

rse member or means for the wire lead which are provided between the winding blocks A and B. At first, a bridge means 20 and its guide means 21, which form the bridge member, will be described. The bridge means 20 is provided by forming a cut-out portion or recess in the middle flange 15AB located between the winding blocks A and B. In close relation to the bridge means or recess 20, the guide means 21 is provided on a bridge section X A at the side of block A. This guide means 21 is formed as a guide piece which connects an edge portion 20a of recess 20 at the winding direction side to the flange 11A 0 of block A in the oblique direction along the winding direction through the section X A .

Next, an inverse engaging means 22 will be now described with reference to FIGS. 7 and 8. If the flange 11B 0 of FIG. 7 is viewed from the right side, the inverse engaging means 22 can be shown in FIG. 8A. In this case, the tip end of one side 13a of recess 12B 1 is formed as a projection which is extended outwards somewhat beyond the outer diameter of flange 11B 0 . The inverse engaging means 22 may take any configuration but it is necessary that when the rotating direction of the bobbin proper 1 is changed to the clockwise direction, the wire lead can be engaged with the recess 12B 1 or projection of one side 13a and then suitably transferred to the next station.

Another guide means 23 is provided on a bridge section X B at the side of winding block B in close relation to the inverse engaging means 22. The guide means 23 is formed as a guide surface which is a projected surface from the bottom surface of section X B and extended obliquely in the winding direction. This guide means or guide surface 23 is inclinded low into the means 22 and has an edge 23a which is continuously formed between the middle flange 15AB and the flange 11B 0 .

In this case, it is possible that the guide means 21 and guide surface 23 are formed to be the same in construction. That is, both the guide means 21 and 23 can be made of either the guide piece, which crosses the winding section or guide surface projected upwards from the bottom surface of the winding section. It is sufficient if the guide means 21 and 23 are formed to smoothly transfer the wire lead from one section to the next section under the bobbin proper 1 being rotated.

Although not shown, in connection with the middle flange 15BC between the winding blocks B and C, there are provided similar bridge means 20, guide means 21, inverse engaging means 22 and another guide means 23, respectively. In this case, since the winding direction of the wire lead is reversed, the forming directions of the means are reverse but their construction is substantially the same as that of the former means. Therefore, their detailed description will be omitted.

According to the bobbin structure of the invention with the construction set forth above, the wire lead, which is transferred from the block A to the section X A by the rotation of bobbin proper 1, is wound on the section X B from the section X A after being guided by the guide piece 21 to the recess 20 provided on the middle flange 15AB, and then transferred to the recess 22 provided on the flange 11B 0 guide surface 23, bridged once to the first section of winding block B through the recess 22 (refer to dotted lines b in FIG. 7). Then, if the rotating direction of the bobbin proper 1 is reversed, the wire lead is engaged with the bottom of recess 22 (refer to solid lines b in FIG. 7). Thus, if the above reverse rotation of bobbin proper 1 is maintained, the wire lead is wound on the block B in the direction reverse to that of block A. When the wire lead is transferred from the block B to block C, the same effect as that above is achieved. Therefore, according to the present invention, the wire lead can be automatically and continuously wound on the bobbin proper 1.

After the single wire lead is continuously wound on blocks A, B and C of bobbin proper 1 as set forth above, the wire lead is cut at the substantially center of each of its bridging portions. Then, the cut ends of the wire lead are connected through diodes Da, Db and Dc at the terminal plates 16, respectively by solder.

In the present invention, the projection piece, which has the diameter greater than that of the flange 11B, is provided in the bridge recess 12 to form the inverse engaging means 22 as described above, so that when the winding direction is changed, the wire lead engages with the inverse engaging means 22 without errors when reversing the winding direction of the wire lead.

If the diameter of the projection piece of means 22 is selected, for example, to be the same as that of the flange 11B, it will not be certain that the wire lead engages with the means 22 because it depends upon the extra length of the wire lead and hence errors in winding cannot be positively avoided.

Further, in this invention, the bridge means is provided on the flange positioned at the bridging portion of the bobbin w hich has a number of dividing blocks separated by flanges, and the inverse engaging means is provided and also the guide means is provided at the former winding section to cooperate with the inverse engaging means. Therefore, the wire lead can be positively fed to the bridge means, and the transfer of the wire lead to the following winding section can be carried out smoothly.

hich has a number of dividing blocks separated by flanges, and the inverse engaging means is provided and also the guide means is provided at the former winding section to cooperate with the inverse engaging means. Therefore, the wire lead can be positively fed to the bridge means, and the transfer of the wire lead to the following winding section can be carried out smoothly.

Further, in this invention since one side of the recess 12 is selected coincident with the tangent of the outer circle of the bobbin proper 1 and also with the winding direction, the wire lead can be smoothly bridged to the following section. Due to the fact that the direction of recess 12 is changed in response to the winding direction, even if there is a block on which the wire lead is wound in the opposite direction to that of the other block, the wire lead can be continuously and automatically wound through the respective blocks.

The above description is given for the case where the present invention is applied to the coil bobbin for the high voltage winding of a fly-back transformer, but it will be clear that the present invention can be applied to other coil bobbins which require divided windings thereon with the same effects.

It will be apparent that many modifications and variations could be effected by one skilled in the art without departing from the spirits or scope of the novel concepts of the present invention, so that the spirits or scope of the invention should be determined by the appended claims only.

SONY TRINITRON KV-1882ME3 CHASSIS SCC-501C-A (XE3) Television receiver which can indicate the numeral of a channel SONY On Screen Display TECHNOLOGY.

A television receiver having a CPU (central processing unit), a ROM (read only memory) in which a program and a font data are written, and a RAM (random access memory) for work area and a shift register. The font data to be indicated as a channel numeral is loaded to the shift register by an interrupt procedure and the output from the shift register is supplied to the video signal system whereby to indicate the channel numeral after the channel is changed.

1. A television receiver for receiving a video signal that includes a synchronizing signal, said receiver comprising:

a central processing unit having an interrupt function;

bus means connected to said central processing unit;

read only memory means connected to said central processing unit through said bus means and containing a contr ol program to be executed by said central processing unit;

ol program to be executed by said central processing unit;

random access memory means connected to said central processing unit through said bus means and used as a work area of said central processing unit;

channel selecting means connected to said central processing unit through said bus means for selecting one of a plurality of channels;

control signal receiving circuit means connected to said central processing unit through said bus means for receiving a control signal and controlling said channel selecting means;

shift register means connected to said central processing unit through said bus means;

clock pulse generating means for supplying a clock pulse to said shift register means synchronized with the synchronizing signal of said video signal and generating a serial signal representing a character pattern from said shift register means; and

mixing means for mixing said video signal and said serial signal;

said control program in said read only memory means containing font data to be displayed, a main program for decoding said control signal and controlling said channel selecting means, and an interrupt program for loading the font data from said read only memory means into said shift register means.

2. A television receiver according to claim 1; further comprising an integrated circuit chip, said central processing unit, said bus means, said read only memory means, said random access memory means and said shift register means being formed on said chip. 3. A television receiver according to claim 1; wherein said synchronizing signal includes a horizontal synchronizing pulse, said central processing unit is interrupted by said horizontal synchronizing pulse, and said interrupt program is started by said horizontal synchronizing pulse. 4. A television receiver according to claim 3; wherein a horizontal trace period follows said synchronizing signal and said font data from said read only memory means is loaded into said shift register means during a first portion of the horizontal trace period and said serial signal is generated during a second portion of the horizontal trace period.BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates generally to a television receiver and more particularly is directed to a television receiver which can indicate the numeral of a channel after the channel is changed.

2. Description of the Prior Art

There is proposed a television receiver in which when a channel is changed, the numeral indicative of the channel after the channel is changed is indicated on the screen of a cathode ray tube during a predetermined period. Such previously proposed television receiver is disclosed in U.S. Pat. No. 3,748,645, U.S. Pat. No. 3,812,285 and so on. A conventional channel indicator used in such television receiver requires a special LSI (large scale integration) chip to indicate the numeral of the channel. However, such LSI chip requires a substantial investment in time and money from its designing to the completion, and when the designing thereof is changed midway, it is quite difficult to cope with such change.

Moreover, it is difficult to give an individuality to the character pattern of the numeral indicating the channel. Furthermore, the number of ICs (integrated circuits) is increased and hence the manufacturing cost is inevitably raise d.

d.

OBJECTS AND SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide an improved television receiver which is free from the problem inherent to the prior art.

It is another object of the present invention to provide a television receiver which can indicate the numeral of a channel after the channel is changed by employing a microcomputer.

It is still another object of the present invention to provide a television receiver in which an individuality can easily be given to the character pattern of the numeral of a channel to be indicated.

It is further object of the present invention to provide a television receiver which can reduce the number of integrated circuits.

According to one aspect of the present invention, there is provided a television receiver comprising:

(a) a central processing unit having an interrupt function;

(b) a bus means connected to said central processing unit;

(c) a read only memory means connected to said central processing unit through said bus means and containing a control program to be executed by said central processing unit;

(d) a random access memory means connected to said central processing unit through said bus means and used as a work area of said central processing unit;

(e) a channel selecting means connected to said central processing unit through said bus means for selecting one of a plurality of channels and producing a video signal; and

(f) a control signal receiving circuit means connected to said central processing unit through said bus means for receiving a control signal and controlling said channel selecting means;

characterized in that said television receiver comprises:

(g) a shift register means connected to said central processing unit through said bus means;

(h) a clock pulse generating means for supplying a clock pulse to said shift register means synchronized with the synchronizing signal of said video signal and generating a serial signal representing a character pattern from said shift register;

(i) a mixing means for mixing said video signal and said serial signal; and

(j) an interrupt means for interrupting an operation of said central processing unit synchronized with a synchronizing pulse of the video signal, said control program in said read only memory means containing a font data to be displayed, a main program for decoding said control signal and controlling said channel selecting means, and an interrupt program for loading the font data from said read only memory means to said shift register means.

The other objects, features and advantages of the present invention will become apparent from the following description taken in conjunction with the accompanying drawings through which the like references designate the same elements and parts.

BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a schematic block diagram of an embodiment of a television receiver according to the present invention;

FIG. 2 is a table showing a 16-bit font data used in the present invention;

FIG. 3 is a diagram showing a screen of the television receiver of the present invention on which a numeral of channel is indicated and waveforms of pulses used in explanation thereof;

FIG. 4 is a diagram showing the format of a remote control signal used in the present invention; and

FIGS. 5 to 8 are respectively flow charts used to explain the operation of the present invention.

DESCRIPTION OF THE PREFERRED EMBODIMENT

Now, an embodiment of a television receiver according to the present invention will hereinafter be described with reference to the attached drawings.

In FIG. 1 showing an example of the present invention, reference numeral 10 generally designates a video signal system, 11 a tuner, 12 a video intermediate frequency (VIF) amplifier, 13 a video detecting c ircuit, 14 a video amplifier and 15 a cathode ray tube, respectively. In this case, the tuner 11 is formed as an electronic tuning system which can receive the video signal of a desired channel by changing a value of a tuning voltage Ec supplied thereto.

ircuit, 14 a video amplifier and 15 a cathode ray tube, respectively. In this case, the tuner 11 is formed as an electronic tuning system which can receive the video signal of a desired channel by changing a value of a tuning voltage Ec supplied thereto.

Reference numeral 20 generally designates a microcomputer, 21 a 4-bit parallel CPU (central processing unit), 22 a ROM (read only memory) in which a program and a font data for indicating a numeral of a channel are written or stored, 23 a RAM (random access memory) for a work area and 31 to 36 input/output ports. These circuits 22 to 36 are connected through a bus 24 to the CPU 21.

Reference numeral 37 designates a 16-bit serial/parallel input and serial output shift register. This shift register 37 is used to generate a signal Sn which indicates the numeral of the channel. To the shift register 37 loaded line by line in parallel is a 16-bit font data indicating the numeral of a channel as, for example, shown in FIG. 2 from the port 32. The font data loaded to the shift register 37 is delievered therefrom in series from MSB (most significant bit) as the signal Sn. At that time, the serial input terminal of the shift register 37 is made at "0" level.

The signal Sn derived from the shift register 37 is supplied to the video amplifier 14 in which the signal Sn is composed on or mixed with the video signal.

The microcomputer 20 together with this shift register 37 is formed as one chip IC (integrated circuit).

Reference numeral 41 designates a D/A (digital-to-analog) converter. The output from the port 31 is supplied to this D/A converter 41 from which the tuning voltage Ec is derived. This tuning voltage Ec is supplied to the tuner 11.

Reference numeral 42 designates a receiving element which receives a remote control signal and 43 its receiving circuit connected theret o. When the remote control signal is, for example, an infrared remote control signal, the receiving element 42 is formed as an infrared ray receiving element and the receiving circuit 43 generates a remote control signal Sr. This remote control signal Sr is the signal which corresponds to an output from a remote control signal transmitter (not shown) and has a format as, for example, shown in FIG. 4. Namely, in this remote control signal, a guide pulse having a pulse width of 2400 μsec exists in the beginning and code pulses of 16 bits from b 0 to b 15 follow the guide pulse with an interval of 600 μsec. In this case the code pulses b 0 to b 15 indicate "0" or "1" in respose to the content of the remote control. When "0", the pulse width is selected as 600 μsec, while when "1", the pulse width is selected as 1200 μsec. This remote control signal Sr is supplied to the port 33.

o. When the remote control signal is, for example, an infrared remote control signal, the receiving element 42 is formed as an infrared ray receiving element and the receiving circuit 43 generates a remote control signal Sr. This remote control signal Sr is the signal which corresponds to an output from a remote control signal transmitter (not shown) and has a format as, for example, shown in FIG. 4. Namely, in this remote control signal, a guide pulse having a pulse width of 2400 μsec exists in the beginning and code pulses of 16 bits from b 0 to b 15 follow the guide pulse with an interval of 600 μsec. In this case the code pulses b 0 to b 15 indicate "0" or "1" in respose to the content of the remote control. When "0", the pulse width is selected as 600 μsec, while when "1", the pulse width is selected as 1200 μsec. This remote control signal Sr is supplied to the port 33.

Reference numeral 44 designates a non-volatile memory which is connected to the port 34 and in which a digital value of the tuning voltage Ec at each channel is stored. Reference numeral 45 designates an input key which is used to change the channel, the sound volume and so on, in which the dynamic scan is carried out by the output from the port 35, and the switching output from which is inputted to the port 36 to detect which key is operated.

Reference numeral 51 designates a synchronizing (sync) separating circuit to which the video signal from the video detector circuit 13 is supplied and from which a vertical synchronizing pulse Pv and a horizontal synchronizing pulse Ph are derived respectively. These pulses Pv and Ph are supplied to the CPU 21 as interrputing signals H-INT and V-INT. The pulse Ph is supplied to a monostable multivibrator 52 which generates a pulse P 52 which becomes "1" from a falling down or trailing edge time point t 1 of the pulse Ph to a start time point t 2 of the display period of the numeral of the channel as shown in FIG. 3 (in which reference numeral 151 designates the screen of the cat hode ray tube). This pulse P 52 is supplied to a gated oscillating circuit 53 as its oscillating control signal so that from the gated oscillating circuit 53 is derived an oscillating pulse P 53 during the period from t 2 to t 4 in which the pulse P 52 is "0" as shown in FIG. 3. This pulse P 53 is supplied to the shift register 37 as the clock. At that time, the frequency of the pulse P 53 is selected as a value corresponding to a dot pitch in the lateral direction of the numeral of the channel to be indicated.

hode ray tube). This pulse P 52 is supplied to a gated oscillating circuit 53 as its oscillating control signal so that from the gated oscillating circuit 53 is derived an oscillating pulse P 53 during the period from t 2 to t 4 in which the pulse P 52 is "0" as shown in FIG. 3. This pulse P 53 is supplied to the shift register 37 as the clock. At that time, the frequency of the pulse P 53 is selected as a value corresponding to a dot pitch in the lateral direction of the numeral of the channel to be indicated.

Accordingly, since the font data on, for example, the first line in FIG. 2 is loaded to the shift register 37 during the first half period from t 1 to t 2 of the 45th horizontal trace period, this font data is extracted from the shift register 37 as the serial signal Sn in response to the pulse P 53 during the second half period from t 2 to t 3 of the above horizontal trace period and then supplied to the video amplifier 14, the numeral of the channel on the first line is indicated on the screen 151 in the interval corresponding to the period from t 2 to t 3 of the 45th line. Although during the period from t 3 to t 4 the pulse P 53 is supplied to the shift register 37, the serial input terminal of the shift register 37 is at "0" level and this "0" level is derived from the shift register 37 during the period from t 3 to t 4 so that no numeral of the channel is indicated on the screen 151 in the interval corresponding to the period from t 3 to t 4 .

When such operation is performed for the 45th to 51st horizontal lines by employing the font data on the 1st to 7th lines shown in FIG. 2, the channel numeral corresponding to the font data in FIG. 2 is displayed as shown in FIG. 3. If the data of all "0" is loaded to the shift register 37 as the font data, the channel numeral is not indicated.

FIGS. 5 to 8 respectively show flow charts of the programs written in the ROM 22 and FIG. 5 shows the main routine thereof.

This main routine shown in FIG. 5 s tarts from a step 501 and in a step 502 the initializing is carried out. Thus, a flag FLG, a buffer BUFF and counters CHCNT, HCNT and WCNT are set in, for example, the RAM 23 and these are all reset (cleared) to "0".

tarts from a step 501 and in a step 502 the initializing is carried out. Thus, a flag FLG, a buffer BUFF and counters CHCNT, HCNT and WCNT are set in, for example, the RAM 23 and these are all reset (cleared) to "0".

A step 503 is such a step in which the existence or not of the remote control signal Sr is judged by the existence or not of the guide pulse, namely, by detecting whether the "1" level of the signal Sr lasts 2400 μsec or not. A step 504 is such a step which judges whether or not there is the input to the key 45, and a step 531 is such a step which judges whether the counter CHCNT is "0" or not. Consequently, when powered, CHCNT=0 is established in the step 502 so that the loop of step 503➝step 504➝step 531➝step 503 is repeated to thereby poll the input of the remote control signal Sr and the input from the key 45. In this case, the counter CHCNT serves as a flag indicative of the existence or not of the request for changing the channel and a timer for setting the displaying period of the channel numeral.

When the remote control signal Sr exists, the bits b 0 to b 15 of the signal Sr are latched in a step 800 and the step is moved to a step 511. Also when an input exists in the step 504, the step 504 moves to the step 511, too. In the step 511, it is judged whether the remote control input in the step 800 and the key input in the step 504 are the commands for changing the channel or not.

When the above inputs are the command for changing the channel, the counter CHCNT is set to "1" in a next step 512. Subsequently, in a step 513, on the basis of the channel data indicated by the remote control signal Sr inputted at the step 800 and the key input in the step 504, a digital tuning voltage data E D for tuning to the channel is read out from the non-volatile memory 44 (see FIG. 1). This digital tuning voltage data E D is outputted to the port 31 in a step 514. Thus, by the analog tuning voltage Ec from the D/A converter 41, the television receiver is set in the receiving state of the channel inputted in the step 800 or 504, thereafter.

In a step 515, from the ROM 22, a font data (data as, for example, shown in FIG. 2) displayed as a numeral of a new channel after the channel is changed is loaded to the buffer BUFF. Although the detail will be described later, the font data in the buffer BUFF is sequentially loaded line by line to the shift register 37 during the 45th to 51st horizontal trace period t 1 to t 2 of each field in accordance with a subroutine 700 shown in FIG. 7. As a result, the channel numeral after the channel is changed is indicated on the screen 151.

When the channel numeral is indicated on the screen 151, the procedure step is returned to the step 503. At that time, since CHCNT=1 is established in the step 512, the procedure step is moved in the order of the step 503➝the step 504➝the step 531➝a step 532. In this step 532, the counter CHCNT is incremented by "1" and in a next step 533, whether the count CHCNT reaches a predetermined value MAX or not is checked where the value MAX is the value corresponding to the period during which the channel numeral is displayed upon changing the channel.

512, the procedure step is moved in the order of the step 503➝the step 504➝the step 531➝a step 532. In this step 532, the counter CHCNT is incremented by "1" and in a next step 533, whether the count CHCNT reaches a predetermined value MAX or not is checked where the value MAX is the value corresponding to the period during which the channel numeral is displayed upon changing the channel.

And, if CHCNT

When CHCNT=MAX is esbalished, the buffer BUFF is cleared to "0" in a step 541. Therefore, since "0" is loaded through the buffer BUFF to the shift register 37 as the font data, Sn="0" is established thereafter so that the channel numeral is not indicated any more.

In a next step 542, the counter CHCNT is reset to "0" and the procedure step is returned to the step 503.

As described above, when the channel change data is inputted, the channel is changed and the channel numeral after the channel is changed is indicated during a constant period.

When the inputs in the steps 800 and 504 are not the commands for changing the channel but the commands for changing, for example, the sound volume, in a step 521 the counter CHCNT is reset to "0" and then in a step 522, the operation based on the commands inputted in the steps 800 and 504 is carried out. The circuitry for executing the procedure except for changing the channel can be made the same as in the prior art and hence it is omitted to show the same in FIG. 1.

On the other hand, FIGS. 6 and 7 respectively show subroutines in which the font data in the buffer BUFF is loaded to the shift register 37. The subroutine 600 shown in FIG. 6 is the interrupt subroutine which is exe cuted when the interrupt procedure is executed by the vertical synchronizing pulse Pv. When the vertical synchronizing pulse Pv is supplied to the CPU 21, this subroutine 600 starts from a step 601 and in a step 602, the counter HCNT is reset to "0". In a step 603, the subroutine 600 is ended and returned to the original main routine.

cuted when the interrupt procedure is executed by the vertical synchronizing pulse Pv. When the vertical synchronizing pulse Pv is supplied to the CPU 21, this subroutine 600 starts from a step 601 and in a step 602, the counter HCNT is reset to "0". In a step 603, the subroutine 600 is ended and returned to the original main routine.

Accordingly, by this subroutine 600, the counter HCNT is reset to "0" at every start point of each field.

The subroutine 700 shows in FIG. 7 is the interrupt subroutine which is executed when the interrupt procedure is executed by the horizontal synchronizing pulse Ph. When the horizontal synchronizing pulse Ph is supplied to the CPU 21, the subroutine 700 starts from a step 701 and in a step 702, a flag FLG indicative of whether the subroutine 700 is executed or not is set to "1". Then, in a step 703, the counter HCNT is incremented by "1". In this case, since the counter HCNT is reset to "0" by the subroutine 600 at every start point of each field and the subroutine 700 is executed at each horizontal syncronizing pulse Ph, the counter HCNT indicates the line number of the horizontal line at each field period.

In a next step 704, the magnitude of the counter HCNT is checked. When 45≤HCNT≤51, in a step 711, the font data in the buffer BUFF (the data as, for example, shown in FIG. 2) is loaded line by line to the shift register 37 from the buffer BUFF each time when the counter HCNT is incremented by "1" each (at every horizontal lines). On the other hand, when 45≤HCNT≤51 is not established, in a step 721, all "0" is loaded to the shift register 37. Then, the subroutine 700 is ended at a next step 712 and returned to the original main routine.

If necessary, the subroutine 700 is provided with a timer routine by which the duration of time necessary for completing the subroutine 700 is set as 40 μsec (the period shorter than the period from t 1 to t 2 ).

Consequently, during the period from t 1 to t 2 in the 45th to 51st horizontal trace periods, by the subroutine 700 the data in the buffer BUFF is loaded to the shift register 37. Then, if the data loaded to the shift register 37 is the font data, the channel numeral is indicated during the period from t 2 to t 3 . While during the period from t 1 to t 2 in other horizontal trace period, the data indicative of all "0" is loaded to the shift register 37 from the buffer BUFF so that the channel numeral during the period t 2 to t 3 is not displayed.

Upon changing the channel, during the predetermined period, the font data regarding the channel numeral after the channel is changed is loaded to the buffer BUFF in the step 515. After that, since the data indicative of all "0" is loaded to the buffer BUFF in the step 541, in accordance with the subroutine 700, during the predetermined period from the change of the channle, the channel numeral after the channel is changed is indicated on the screen 151 as shown in FIG. 3. After the predetermined period elapses, the display is not carried out any more.

FIG. 8 shows a su broutine 800 which is used to read the remote control signal Sr. This subroutine 800 starts from a step 801. In a next step 802, a pointer i is reset to "0" and in a succeeding step 811, a delay corresponding to the "0" level period of 600 μsec between the trailing edge of the guide pulse and the rising edge of the bit b 0 (see FIG. 4) is carried out. Further, in a next step 821, the counter WCNT is reset to "0". In this case, the pointer i indicates a particular bit of the bits b 0 to b 15 of the remote control signal Sr and i=0 to 15. Also, the counter WCNT is used to check the respective pulse widths of the bits b 0 to b 15 .

broutine 800 which is used to read the remote control signal Sr. This subroutine 800 starts from a step 801. In a next step 802, a pointer i is reset to "0" and in a succeeding step 811, a delay corresponding to the "0" level period of 600 μsec between the trailing edge of the guide pulse and the rising edge of the bit b 0 (see FIG. 4) is carried out. Further, in a next step 821, the counter WCNT is reset to "0". In this case, the pointer i indicates a particular bit of the bits b 0 to b 15 of the remote control signal Sr and i=0 to 15. Also, the counter WCNT is used to check the respective pulse widths of the bits b 0 to b 15 .

After the delay of 70 μsec is performed in a succeeding step 822, whether the flag FLG is "0" or "1" is checked in a next step 823. When FLG=0, namely, the interrupt procedure is not executed, the counter WCNT is incremented by "1" in a following step 824. When FLG=1, namely, the interrupt procedure is executed, the counter WCNT is incremented by "2" in a step 825 and the processing time due to the interrupt procedure is corrected. Thereafter, the flag FLG is reset to "0" in a next step 826. Then, in a step 827, it is checked whether the level of ith bit of the remote control signal Sr reaches the "0" level or not, namely, whether ith bit is ended or not. When ith bit is not ended, the step 827 returns to the step 822, while when ended, the step 827 advances to a step 831.

Accordingly, during the period in which the level of ith bit of the signal Sr is at the "1" level, the loop from the steps 822 to 827 is repeated. Upon repeating the loop from the steps 822 to 827, if the interrupt subroutine 700 is not executed at all, the FLG=0. Therefore, in the steps 822 and 824, the counter WCNT is incremented by "1" each at every 40 μsec. Thus, at the time when the above loop is ended, if ith bit is "0" (namely, the pulse width is 600 μsec), WCNT=15, while if ith bit is "1" (namely, the pulse width is 1200 μsec), WCNT=30 (the processing time necessary for other steps is neglected for simplicity).

Upon repeating this loop from the steps 822 to 827, if the interrupt subroutine 700 is executed, 40 μsec is consumed to execute such subroutine. This is the same as that necessary for executing the step 822 once. Also, at that time, since FLG=1 (step 702), the counter WCNT is incremented by "2" in the step 825. As a result, at the time when this loop is ended, if ith bit is "0", WCNT=15, while if ith bit is "1", WCNT=30.

After the above loop is ended, the counter WCNT is checked in the step 831. If WCNT≤15, the level "0" of ith bit is set in the RAM 23 in a step 832, while if WCNT>15, the level "1" of ith bit is set in the RAM 23 in a step 833. In a next step 834, whether the above procedure is executed for all the bits of the remote control signal Sr or not is checked by the pointer i. When the above procedure is not yet executed for all the bits, the pointer i is incremented by "1" in a step 835 and then the step 835 returns to the step 811. On the contrary, when the above procedure is executed for all the bits, the step 834 advances to a step 841.

In the step 841, the remote control signal Sr is judged on the basis of the data in the steps 832 and 833. And, in a step 842, this subroutine 800 is ended and returned to the original main routine.

As set forth above, according to the present invention, it is possible to perform the change of the channel and to indicate the channel numeral at that time. In this case, particularly in accordance with the present invention, the change of the channel and the indication of the channel numeral after the channel is changed are carried out by the use of the ordinary microcomputer 20 so that the time and cost necessary from designing to completing can be reduced extremely. Moreover, when the designing is changed in the midway thereof, the designing can be changed with ease.

Further, the individuality can be given to the character pattern of the numeral of the channel to be indicated with ease. Also, since the number of the ICs can be reduced, this is advantageous for reducing the manufacturing cost and for increasing reliablity.

In addition, in the above description, it is possible to provide the steps 531 to 542 in the subroutine 600.

The above description is given on a single preferred embodiment of the invention, but it will be apparent that many modifications and variations could be effected by one skilled in the art without departing from the spirits or scope of the novel concepts of the invention, so that the scope of the invention should be determined by the appended claims only.

SONY Automatic pre-programming system for TV receiver/ Automatically presetting channel Program selecting system :

"A channel selecting system for use in a receiver having a voltage controlled tuning element which has an automatic channel presetting function which utilizes a pulse generator and a binary counter connected to the generator to count the pulses and to generate a binary coded output in accordance with the sum of the pulses. A digital-to-analog converter changes the binary coded output into a linearly increasing tuning sweep voltage which in turn conditions the voltage controlled tuning element to scan the frequency range of the tuner as the tuning voltage increases. As the frequencies are scanned, a detector, connected to the tuning element, senses the presence of a broadcast channel. When a channel is detected, the scan is interrupted and a binary memory is utilized to store the binary coded output which corresponds to the frequency of the detected broadcast channel. A control gate signal generator driven by the detector controls the pulse generator and memory such that the scan is continued until the entire frequency range has been scanned. Channel selection is accomplished by switch means actuatable to address the memory to read out a selected binary code output corresponding to the channel desired which causes the converter to generate a voltage to condition the tuning element to tune to the desired frequency. The voltage control tuning element may comprise several different elements, one for each of a plurality of different frequency ranges. Means are provided for selecting an appropriate tuner such that channels from any of the frequency ranges may be selected. "

An automatic tuning scheme for use in TV receivers includes a start/stop circuit which creates a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively, a tuning voltage generator which generates a gradually varying tuning voltage under control of the search start signal and search stop signal, and a memory circuit for storing the tuning voltage from the generator when desired. The tuning voltage stored in the memory circuit is supplied to a tuner including a well known voltage-sensitive capacitance diode.

1. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:

start/stop circuit means for creating a search start signal and a search stop signal upon the receipt of a search start instruction and the presence of a detected incoming signal, respectively, the presence of a detected incoming signal being determined at least in part in response to an output of said AFT detector;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

memory circuit means for storing the tuning voltage from said tuning voltage generator means;

signal decision circuit means for determining whether the detected incoming signal is a true television signal including a television synchronizing signal by detecting the presence of the television synchronizing signal and the search stop signal, said signal decision circuit means providing a memory store instruction for the memory circuit means in the presence of the true television signal and providing a search re-start instruction for the start/stop circuit means in the absence of the true television signal, the tuning voltage stored in the memory circuit means being supplied to a tuner including a voltage-sensitive capacitance diode.

2. The automatic tuning scheme according to claim 1 further comprising a memory skip circuit for inhibiting the supply of the memory store instruction to the memory circuit and skipping an undesired broadcasting station. 3. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:start/stop circuit means for creating a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

memory circuit means for storing the tuning voltage from the tuning voltage generator means

means for detecting the presence of synchronizing signals within the detected incoming signal;

noise skip circuit means which determines whether the detected synchronizing signal is a true synchronizing signal or noise and provides a search re-start instruction for the start/stop circuit means in the presence of noise; and

signal decision circuit means for determining whether there is a true television signal by counting the number of the true synchronizing signals derived from the noise skip circuit means and counting a predetermined number of the true synchronizing signals in a predetermined period of time, and then providing a memory store instruction for the memory circuit means in the presence of the true television signal and a search re-start instruction to the start/stop circuit means in the absence thereof, the tuning voltage stored in the memory circuit means being supplied to a tuner.

4. In an automatic tuning scheme for use in TV receivers including an AFT detector, which produces search start and stop signals upon receipt of a search start instruction and a detected incoming signal, a combination comprising:means for detecting the presence of synchronizing signals within the detected incoming signal;

noise skip circuit means for determining whether the synchronizing signal is a true synchronizing signal or noise and provides a search restart instruction to said tuning scheme in the presence of noise; and

means for adjusting a skip level in the noise skip circuit means in accordance with the intensity of the detected incoming signal.

5. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:start/stop circuit means which creates a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

memory circuit means for storing the tuning voltage from the generator, the tuning voltage stored in the memory circuit means being supplied to a tuner;

speed changer means for reducing the rate of variation in the tuning voltage derived from the tuning voltage generator means to enable a low speed searching operation slower than that of the normal searching operations when detecting an AFT detector output;

means for detecting the presence of synchronizing signals within the detected incoming signal; and

means for determining whether the synchronizing signal is a true synchronizing signal or noise and providing a search re-start instruction to said tuning scheme in the presence of noise.

6. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:start/stop circuit means for creating a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

memory circuit means for storing the tuning voltage from the tuning voltage generator means, the tuning voltage stored in the memory circuit means being supplied to a tuner; and

speed changer means for reducing the rate of variation in the tuning voltage derived from the tuning voltage generator means to enable a low speed searching operation slower than that of the normal searching operation when detecting an AFT detector output, the direction of variation of the tuning voltage being reversed in accordance with the polarity of the AFT detector output.

7. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:start/stop circuit means for creating a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

memory circuit means for storing the tuning voltage from the tuning voltage generator means, the tuning voltage stored in the memory circuit means being supplied to a tuner;

out-of-tuning detector means for supplying a search re-start signal to the start/stop circuit means when detecting the out-of-tuning condition;

means for detecting the presence of synchronizing signals within the detected incoming signal; and

means for determining whether the synchronizing signal is a true synchronizing signal or noise and providing a search re-start instruction to said tuning scheme in response thereto.

8. The automatic tuning scheme according to claim 7 wherein the out-of-tuning condition is sensed by comparing the AFT detector output to a given reference voltage. 9. An automatic tuning scheme for use in TV receivers including an AFT detector comprising:start/stop circuit means for creating a search start signal and a search stop signal upon the receipt of a search start instruction and a detected incoming signal, respectively;

tuning voltage generator means for generating a gradually varying tuning voltage under control of the search start signal and search stop signal;

means for detecting the presence of synchronizing signals within the detected incoming signal; and

means for determining whether the detected synchronizing signal is a true synchronizing signal or noise and providing a search re-start instructions to said tuning scheme in the presence of noise.

10. The automatic tuning scheme according to claim 9 further comprising alarm means enabled by the tuning instruction for notifying the operator of the automatic tuning operation. 11. The automatic tuning scheme according to claim 10 wherein said alarm means release alarm signals in the form of sound. 12. The automatic tuning scheme according to claims 3, 4, 5, 6, 7, or 9 wherein the reception of a true television signal is determined by the use of said true synchronizing signal and an AFT output.BACKGROUND OF THE INVENTION

The present invention relates to an automatic pre-programming tuning circuit which performs tuning operation automatically.

It is customary to perform the tuning operations in TV receivers while a viewer manually rotates a tuning knob. However, the tuning operation is bothersome particularly in case of the continuously varying tuning operation such as in UHF reception. Though tuning operation is considerably simpler in case of TV receivers of the recently developed touch control type or remote control type, it is difficult for a non-skilled person the to preset tuning operation, namely, to adjust the tuning frequencies for respective broadcasting stations before starting to watch a TV receiver.

SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide an automatic tuning scheme which enables automatic preselectable tuning operation by sequentially memorizing tuning voltages of respective automatically selected broadcasting channels.

In its broadest aspect, an automatic tuning device of the present invention comprises a tuning voltage generator which generates a tuning voltage gradually variable during tuning operation, a memory circuit which receives the tuning voltage derived from the generator upon receipt of normal reception signals and memorizes a plurality of discrete tuning voltages each associated with a respective one of normal reception signal corresponding to a serviceable broadcasting station and means for picking up selectively one of the discrete tuning voltages from the memory circuit and supplying it to a tuner.

BRIEF DESCRIPTION OF THE DRAWINGS

Other objects and attendant advantages of the present invention will be easily appreciated as the same becomes better understood by reference to the following detailed description when considered in conjunction with the accompanying drawings in which like reference numerals designate like part throughout the figures thereof, and wherein:

FIG. 1 is a schematic diagram of the automatic tuning apparatus embodying the present invention;

FIG. 2 is a more detailed circuit diagram of the automatic tuning apparatus shown in FIG. 1;

FIG. 3 is a schematic diagram of another embodiment of the present invention;

FIGS. 4 and 5 are a circuit diagram and a waveform diagram showing a noise skip circuit included in FIG. 3 embodiment;

FIG. 6 is an improvement in the noise skip circuit shown in FIGS. 4 and 5;

FIGS. 7 and 8 are embodiments effective to modify the searching speed in the automatic tuning apparatus;

FIGS. 9 through 11 are refresh means effective in the automatic tuning apparatus of the present invention;

FIG. 12 shows another embodiment including a memory skip circuit effective in the automatic tuning apparatus;

FIGS. 13 and 14 show alarm means effective in the automatic tuning apparatus.

DETAILED DESCRIPTION OF THE INVENTION

A basic circuit of a TV recei ver having an automatic tuning scheme implemented with the present invention is shown in FIG. 1, which includes an antenna 1, a tuner 2, an intermediate frequency (IF) circuit 3, an automatic fine tuning (AFT) circuit 4, a video circuit 5, a synchronizing separator 6, a deflection circuit 7, a picture tube 8. According to the present invention, a start/stop circuit 9, a tuning voltage generator 10, a memory circuit 11 and a signal decision circuit 12 are further provided to form the automatic tuning scheme of the present invention.

ver having an automatic tuning scheme implemented with the present invention is shown in FIG. 1, which includes an antenna 1, a tuner 2, an intermediate frequency (IF) circuit 3, an automatic fine tuning (AFT) circuit 4, a video circuit 5, a synchronizing separator 6, a deflection circuit 7, a picture tube 8. According to the present invention, a start/stop circuit 9, a tuning voltage generator 10, a memory circuit 11 and a signal decision circuit 12 are further provided to form the automatic tuning scheme of the present invention.

It will be noted that the tuner 2 can be implemented with a well known electronic tuning circuit which includes a voltage-sensitive capacitance diode as disclosed in U.S. Pat. No. 3,233,179 entitled "AUTOMATIC FINE TUNNING CIRCUIT USING CAPACITANCE DIODES" issued on Feb. 1, 1966.

If the start/stop circuit 9 is given a search start command or au automatic tuning instruction prior to effecting of the preset tuning operation, then the start/stop circuit 9 will develop a search start pulse which is turn is supplied to the tuning voltage generator 10. Under the circumstance the tuning voltage generator 10 develops a sweep voltage or staircase voltage which is gradually rising or dropping during the automatic tuning operation. The sweep or staircase voltage is supplied as the tuning voltage to the tuning capacitance diode in the tuner 2 by way of the memory circuit 11. This implies that the reception frequency in the tuner 2 is gradually varied.

In this way, when the television signal of a specific broadcasting channel is received, the television video signal is derived from the IF circuit 3 and the synchronizing signal from the synchronizing separator 6. These signals are applied to the start/stop circuit 9. Meantime, the AFT detector output is derived from the AFT circuit 4 and supplied to the start/stop circuit 9.

More particularly, when the television signal is accurately received, the AFT detector output voltage will change in polarity so that the start/stop circuit 9 is permitted to develop a search stop pulse and the vertical synchronizing signal. In the given example the vertical synchronizing signal may serve as the search stop pulse. The search stop pulse is supplied to the tuning voltage generator 10, barring the generator 10 from developing the sweep or staircase voltage. The voltage at this moment remains unchanged since then and keeps being supplied as the tuning voltage to the tuner 2 via the memory circuit.

The vertical synchronizing signal derived from the start/stop circuit 9 is supplied to the signal decision circuit 12 to determine as to whether the signal being received is a normal or true television signal. If the affirmative answer is given, then the signal decision circuit 12 will issue a memory instruction which in turn is supplied to the memory circuit 11 so that the instantaneous tuning voltage derived from the generator 10 is stored within the memory circuit 11.

Contrarily, if a false synchronizing signal is derived from the start/stop circuit 9, then the signal decision circuit 12 reacts to it so that the circuit 12 issues a search re-start pulse. This is supplied to the start/stop circuit 9 to repeat the same procedure as when executing the first search start pulse. The procedure is repeated in this manner until the start/stop circuit 9 recognizes a true television vertical synchronizing signal or accurate reception is available by the tuner 2.

In other words, the memory instruction is not issued from the signal decision circuit 12 until the optimum reception state is guaranteed. Upon issuance of the memory instruction the instantaneous tuning voltage is stored in the memory circuit 11 and subsequently supplied to the tuner 2.

Once the preset tuning operation (i,e, the presetting of the optimum reception frequency) has been completed for the specific broadcasting channel, the tuning voltage stored in the memory circuit 11 will be automatically supplied to the tuner in response to release of a tuning instruction from an operational panel of the known touch control type or remote control type. The searching procedure is not required at this time.

It is obvious that the memory circuit 11 shown in FIG. 1 includes a predetermined number of memory elements the number of which corresponds to the number of serviceable broadcasting stations. The same searching or presetting procedure is repeated when it is desired to search and memorize a predetermined number of discrete tuning voltages prior to use of a TV receiver.

As noted earlier, when the search start instruction is given and the search start signal is released from the start/stop circuit 9, the tuning voltage generator 10 starts generating the sweep voltage (or the staircase voltage), which is supplied to the tuner 2 via the memory circuit 11 while showing a gradual variation. Alternatively, the gradually varying voltage may be supplied to the tuner 2 directly. If the search stop signal is derived from the start/stop circuit 9 upon receipt of the television signal, the sweep voltage generating function of the tuning voltage generator will come to a halt. The instantaneous tuning voltage supplied to the tuner 2 is held unchanged for a while.

At this time the signal decision circuit 12 decides whether the received signal is true or false. After confirming the presence of the true television signal, the memory instruction is issued for the memory circuit 11 so that the tuning voltage available from the tuning voltage generator 10 is held within the memory circuit 10 to complete the presetting of the optimum reception frequency for the specific television station.